你可以在这里下载到模拟题题面:

你可以在这里下载到我的指令系统和汇编代码:

INL RD,从 IO 单元的低 8 位获得数据,并存入通用寄存器 RD。

显然,这是一个 8 位的指令:

- 第 1~3 位是我定义的指令码,不妨取 001

- 第 4 位是 0

- 第 5~6 位是 RS, 在这里取任意值,不妨取00

- 第 7~8 位是 RD

0010XXRD。

在设计指令的时候,0010 的散转地址是 640,因此,可以令INL RD这句指令的指令码是 20。

需要注意的是,INL R0、INL R1、INL R2、INL R3的微指令必须不同,但是他们产生的微地址必须相同,这意味着,前 4 位必须是 0010,即 16 进制下的 2,而后 4 位必须不同,同时需要保证,最后 2 位用 00 表示 R0、01 表示 R1、10 表示 R2、11 表示 R3。

那么,指令就可以写成:

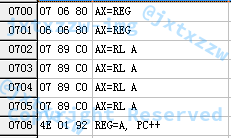

INL R0 20 1 INL R1 21 1 INL R2 22 1 INL R3 23 1

在微程序的设计中,源地址选择 IOR,目的地址选择 RWR。

这是单条微指令,所以执行后 PC 递增,且结尾变址。

关键是总线规则。

为了使得 DX 和 CX 都能作为目标寄存器,那 OP 必须为 0,同时,IO 单元是需要取出低字节,所以总线规则应该是偶字节送出,由于目标寄存器是由 RD 指定的,所以目标寄存器可以看作只有 8 位,所以送到高字节就好了。因此,总线规则是 010。

测试,结果正确,不管 RD 取值为何,都能得到正确的结果。

INH RD,从 IO 单元的高 8 位获得数据,并存入通用寄存器 RD。

类似的,区别只是需要注意总线规则是奇送奇。

0100RSXX。

INH R0 40 1 INH R1 41 1 INH R2 42 1 INH R3 43 1

OUTL RS,将通过寄存器 RS 的数据送出到 IO 单元的低 8 位。

0110RSXX。

类似,需要注意 RS 的取值,即后 4 位为 0000、0100、1000、1100。

OUTL R0 60 1 OUTL R1 64 1 OUTL R2 68 1 OUTL R3 6C 1

SWITCH RD,将 RD 中高 4 位和低 4 位的值交换,并存回 RD。

例如,原来的数值为 0xA3,则交换后为 0x3A。

如果是高 8 位和低 8 位交换,那就相对简单,只要 R0->TMP、R1->R0、TMP->R1 即可。

现在是 4 位,最先想到的是位运算,但是位运算显然不合要求,首先就没有办法把需要进行位运算的掩码值存进去。

可以用循环位移。

例如原来是 1234,希望变成 1243,那么可以首先将 RD 的低 8 位复制到 AX 的低 8 位、将 RD 的低 8 位复制到 AX 的高 8 位,此时 AX 为 3434,只要通过循环左移得到 4343 即可。

于是,循环左移 4 次。

得到 ALU 的运算结果以后,将 ALU 的低 8 位赋值给 RD 的低 8 位即可。

总线规则取偶送奇。

JMPL RS,跳转到寄存器 RS 中值所指向的地址执行机器指令。

只考虑实现这个指令,是非常简单的,甚至比之前的JMP *更简单,因为只要令 RS 寄存器的值覆盖掉 PC 的值即可。

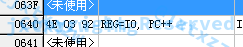

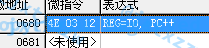

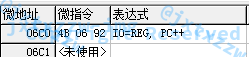

但是并不是简单地令源地址为 RRD、目的地址为 PC。需要注意的是只能把 REG 的低字节赋值给 PC 的低字节,且需要将 PC 的高字节置为 00。

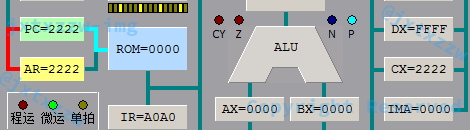

如图便是错误的示例。

可以考虑先把 REG 的低字节丢到 BX 中,然后 B->PC。

现在的问题是怎么实现汇编程序。

data segment ;将程序装载到数据存储器

assume ds:data

org 0

start:

INH R3

INL R0

INH R1

SWITCH R0

OUTL R0

JMPL R3

data ends

end start

由于题目说,不能预先给内存区域赋值,但是不包括寄存器,所以可以令 R3 的值为 JMPL 到的地址,显然,循环的部分是从 SWITCH 到 JMPL,所以可以令 R3 的初值为 03。

注意到,IN 的操作已经不影响整个循环的流程,所以可以令 R3 的初值为 01。

特别的,如果 INH 的高位为 00,那么,R3 就可以不用设置,每次 JMP 到 RS 的高位即可。

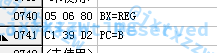

INL R0 20 1 INL R1 21 1 INL R2 22 1 INL R3 23 1 INH R0 40 1 INH R1 41 1 INH R2 42 1 INH R3 43 1 OUTL R0 60 1 OUTL R1 64 1 OUTL R2 68 1 OUTL R3 6C 1 SWITCH R0 80 1 SWITCH R1 85 1 SWITCH R2 8A 1 SWITCH R3 8F 1 JMPL R0 A0 1 JMPL R1 A4 1 JMPL R2 A8 1 JMPL R3 AC 1

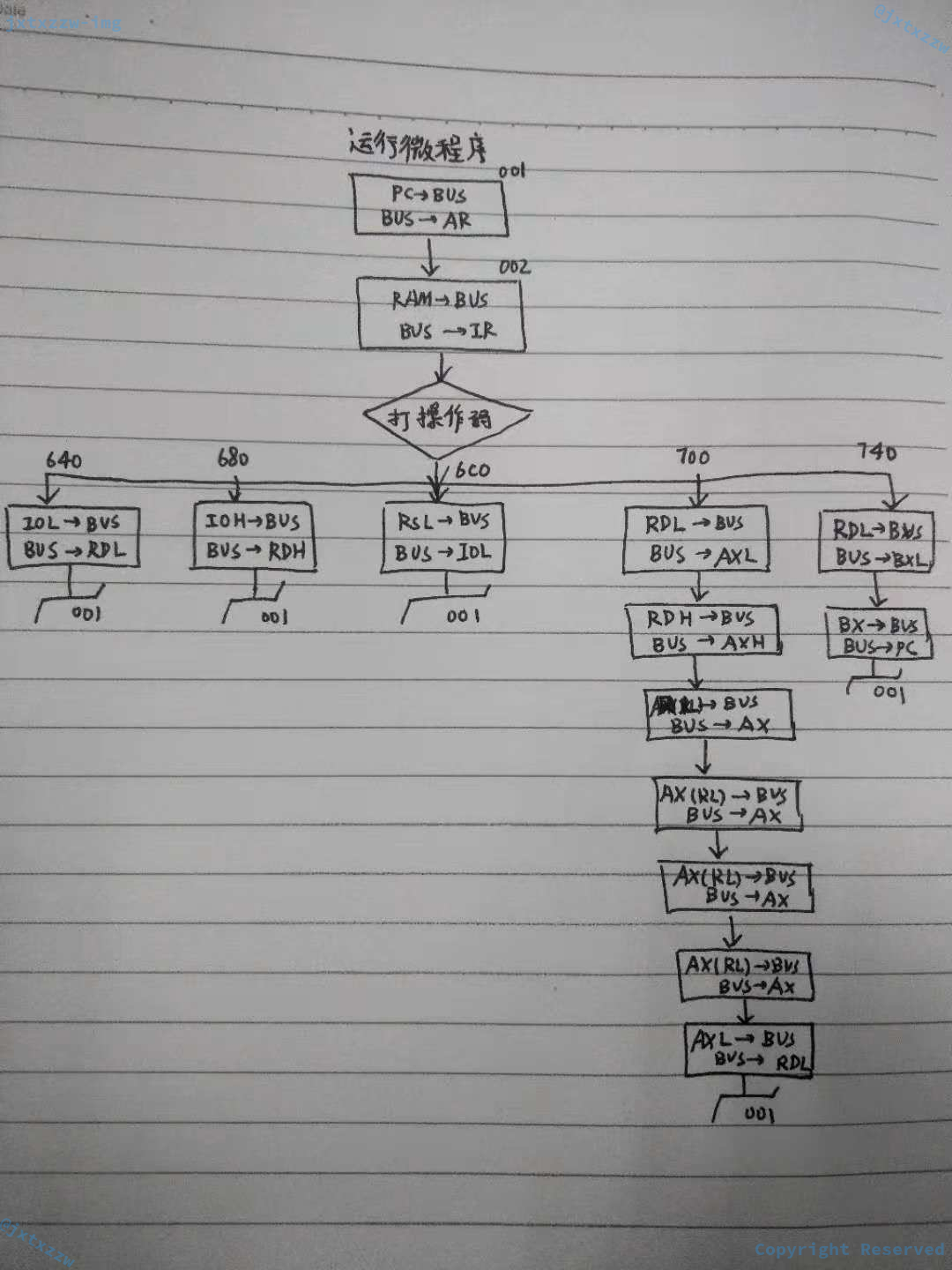

流程图如下:

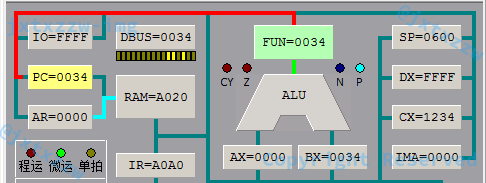

下载的代码中没有微地址为0741的微指令,我补了一下发现只有在字传递的时候PC的前两位才是0(设CX为1234,则PC为0034,不是字传递时PC为3434),不知道是不是正常现象,感觉用奇偶传递应该也能实现的样子。

@YaK方法应该不止一种,能得到正确的结果就行。不过我们学校用的这个软件在奇偶传递的时候确实有 BUG,感觉是软件开发商的问题。

请问不用在流程图里说明PC+1吗?

@mmm你好,要的,需要在流程图里说明 PC++,特别的,对于带有 ADDR 的指令,可能会有多个 PC++。

牛牛大佬

牛牛巨佬

谢谢分享~

好棒!

感谢学长分享!

诶呦不错哦

好极了ヾ ^_^♪

thank!!

thanks

tql