Visits: 1041

请完成如下实验,并总结规律:

设计机器指令 INL DR,实现从Input的低8位输入数据到DR寄存器。并通过设置不同的W,XP,OP值,验证Input到DR的数据通路。

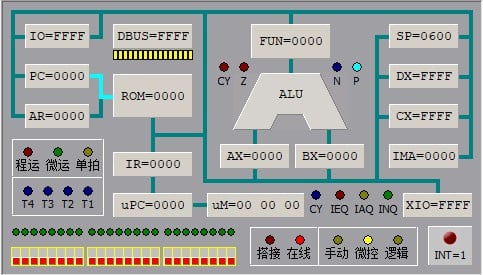

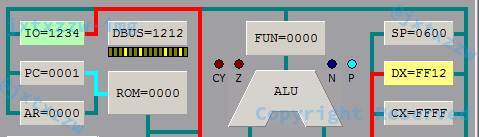

实验开始前,设置Input的值为1234h,完成下表:

首先,明确微指令的组成是,前3位为操作码、第4位固定0或者1,第5~6位为RS,第7~8位是RD。

由题目要求,显然,第5~6位是任意值,第7~8位是RD。

那么,应该是4位散转,第4位取0。

由此,指令格式为0010XXRD。

其中前3位是指令操作码,不妨令INL为001。XX表示任意值,不妨取XX为00。

特别的,RD的取值为R0(00)、R1(01)、R2(10)、R3(11)。

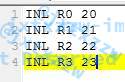

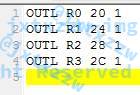

基于以上的分析可得,INL R0为00100000、INL R1为00100001、INL R2为00100010、INL R3为00100011。

显然,这四条指令在指令系统中必须分写四条(因为软件不认识 INL RD这样的写法),但是在微程序中他们一定做的是同一件事,这意味着微地址散转一定是同一个地址。

那么,我们令Ids为1,取4位散转即可。这样的话,对于上面4条指令(20、21、22、23),散转地址都是640。对应的,可以写出指令系统。这些指令的长度都为1。

在微程序,应该令源选择IOR,目的选择通用寄存器,然后按要求分别设置不同的W,XP,OP值。

在640的地方,选择从I/O到通用寄存器。

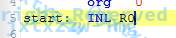

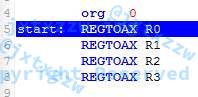

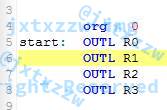

编写汇编代码,然后装载运行。

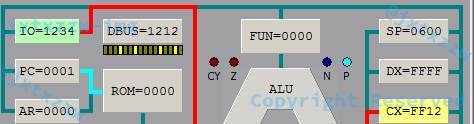

然后尝试先令W,XP,OP为0、0、0,可以看到,这是一个奇到奇的传递,且观察到选通的通用寄存器是CX,值为FF12,并没有选通DX。

尝试先令W,XP,OP为0、0、1,可以看到,这是一个奇到偶的传递,且观察到选通的通用寄存器是CX,值为FF12,并没有选通DX。

类似地,修改W、XP、OP的值,可以得到INL R0剩下的几组记录。

特别需要注意的是,W、XP、OP取值为1、0、1的时候,CX是1212。W、XP、OP取值为1、1、0的时候,总线规则没有信息显示。

之后修改汇编代码的R0为R1,重复上面的步骤,记录INL R1的结果。

与之前的结果比较,可以看到,这次奇字节和偶字节的传递比较符合预期,不像之前那个一样只有传到最低位。

特别需要注意的是,W、XP、OP取值为1、0、1的时候,CX还是1212。W、XP、OP取值为1、1、0的时候,似乎是寄存器是CL就接受INL、寄存器是CH就接受INH。

下面尝试DX,即R2和R3。

只需要修改汇编代码的R1为R2,其他都不需要修改,重复上面的步骤。

观察到成功选择了DX。

但是当W、XP、OP取值为0、0、1的时候,却又选回了CX。

这是因为,如果要选通DX,那么OP的值必须为0,当且仅当OP的值为0的时候,设置的RD才会对R2和R3有效。

这也就意味着,后面的尝试中,所有的OP取值为1的,都可以不用尝试了,那些选的都是CX。

类似地,执行INL R3的时候,发现奇->奇、奇->偶都比较正常。

最后的结果如下表。

| W|XP|OP取值 | 总线规则 | INL R0 | INL R1 | INL R2 | INL R3 |

|---|---|---|---|---|---|

| 000 | 奇->奇 | CX=FF12 DX=FFFF | CX=12FF DX=FFFF | CX=FFFF DX=FF12 | CX=FFFF DX=12FF |

| 001 | 奇->偶 | CX=FF12 DX=FFFF | CX=FF12 DX=FFFF | CX=FF12 DX=FFFF | CX=FF12 DX=FFFF |

| 010 | 偶->奇 | CX=FF34 DX=FFFF | CX=34FF DX=FFFF | CX=FFFF DX=FF34 | CX=FFFF DX=34FF |

| 011 | 偶->偶 | CX=FF34 DX=FFFF | CX=FF34 DX=FFFF | CX=FF34 DX=FFFF | CX=FF34 DX=FFFF |

| 100 | 奇->奇 | CX=FF12 DX=FFFF | CX=12FF DX=FFFF | CX=FFFF DX=FF12 | CX=FFFF DX=12FF |

| 101 | 奇->偶 | CX=1212 DX=FFFF | CX=1212 DX=FFFF | CX=1212 DX=FFFF | CX=1212 DX=FFFF |

| 110 | CX=FF34 DX=FFFF | CX=12FF DX=FFFF | CX=FFFF DX=FF34 | CX=FFFF DX=12FF | |

| 111 | 字传递 | CX=1234 DX=FFFF | CX=1234 DX=FFFF | CX=1234 DX=FFFF | CX=1234 DX=FFFF |

结论:

1、 指令系统最后2位决定的是R0~R3中的哪一个。他们的指令码不一样、散转地址一样,程序会在执行的时候自动选择是哪一个通用寄存器。

2、 当选择的是寄存器的低位时,源的奇偶字节正常工作,但是目的寄存器的奇偶字节无论怎么选择都只会存入低字节。当选择的是寄存器的高位时,源和目的的奇偶字节正常工作。

3、 如果要选择DX,OP必须为0。这也意味着很多操作在选择DX时是无法完成的,必须通过其他手段(例如分步)完成。

4、 特别注意W、XP、OP为1、1、0这组情况,是自动。即目的寄存器选的是低位,那么就自动把源的低位存放进去;目的寄存器选的是高位,那么就自动把源的高位存放进去。

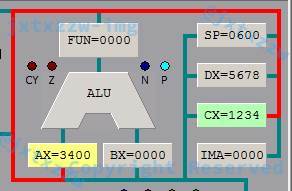

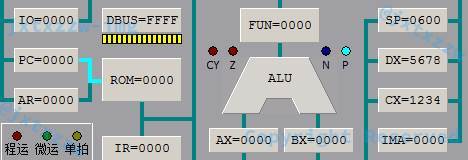

在微程序中设计相关微指令(不一定要设计机器指令对应的微程序),验证RS的数据进入AX时,W, XP和OP的作用。实验开始前,设置CX=1234h,DX=5678h。完成下表:

与上一题类似,尝试W、XP、OP的不同取值。

首先明确微指令,还是和上面一样,指令码不妨就定001、第4位取0、第5~6位是源寄存器,即R0~R3(00、01、10、11),第7~8位任意,不妨取00。

由此,0010RS00。

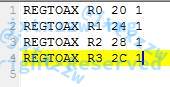

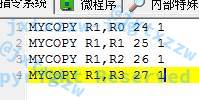

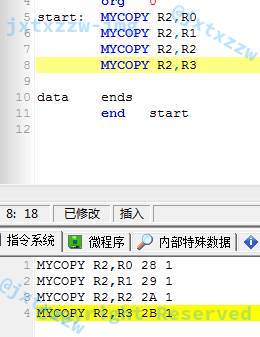

根据上面的分析,指令码分别为20、24、28、2C。

在微程序中,源编码选择通用寄存器RRD,目的编码选择AX。

观察得到结果。

这里为了方便操作,对微程序做如下修改:

第一步还是按照要求执行RS->AX,但是在执行以后,马上执行IOR->AX,这样,只要令I/O为0000,之后每次运行后执行的IOR->AX都相当于是对AX进行了复位,可以正常执行下面的指令而不用担心上一次的结果残留影响观察。

这样,在执行完指令以后,一次记录一行中的4个结果,然后修改W、XP、OP的值,继续。

结果如下:

| W|XP|OP取值 | 总线规则 | R0->AX | R1->AX | R2->AX | R3->AX |

|---|---|---|---|---|---|

| 000 | 奇->奇 | 3400 | 3400 | 3400 | 3400 |

| 001 | 奇->偶 | 0034 | 0034 | 0034 | 0034 |

| 010 | 偶->奇 | 3400 | 1200 | 7800 | 5600 |

| 011 | 偶->偶 | 0034 | 0012 | 0078 | 0056 |

| 100 | 奇->奇 | 3400 | 3400 | 3400 | 3400 |

| 101 | 奇->偶 | 3434 | 3434 | 3434 | 3434 |

| 110 | 1200 | 1200 | 5600 | 5600 | |

| 111 | 字传递 | 1234 | 1212 | 5678 | 5656 |

结论:

1、 指令系统第5~6位决定的是R0~R3中的哪一个。他们的指令码不一样、散转地址一样,程序会在执行的时候自动选择是哪一个通用寄存器。

2、 当DX作为源寄存器的时候,XP值必须为1,否则只能选择CX。

3、 在RS->AD操作中,奇偶字节与高低字节,在源和目的寄存器上是相反的。

4、 自动的总线规则,由于AX默认选择高位,所以就自动只传递高位。

5、 字传递的总线规则当选择高位时能够复制整个字、否则会复读某两位。

设计机器指令MOV RS, RD,实现将源寄存器RS的内容复制到目标寄存器RD。并通过设置不同的W, XP和 OP值验证数据通路。

实验开始前,设置CX=1234h,DX=5678h。完成下表:

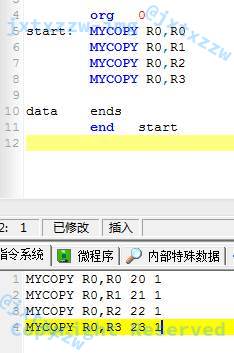

指令叫MYCOPY,格式为0010RSRD。

那么,如果是MYCOPY R0,R0,就是00100000,就是20。类似地,MYCOPY R0,R1,就是00100001,就是21。

微程序也非常简单,就是源寄存器到目的寄存器。

观察到,CX和DX的值都没有发生变化。

继续修改W、XP、OP取值,重复。

之后修改指令系统,改源为R1、R2、R3,重复。

| RS->RD | W|XP|OP取值 | |||||||

|---|---|---|---|---|---|---|---|---|

| 000 | 001 | 010 | 011 | 100 | 101 | 110 | 111 | |

| R0->R0 | CX=1234 DX=5678 | CX=1234 DX=5678 | CX=1234 DX=5678 | CX=1234 DX=5678 | CX=1234 DX=5678 | CX=3434 DX=5678 | CX=1234 DX=5678 | CX=1234 DX=5678 |

| R0->R1 | CX=1234 DX=5678 | CX=1212 DX=5678 | DX=3434 DX=5678 | CX=1234 DX=5678 | CX=1234 DX=5678 | CX=1212 DX=5678 | CX=1234 DX=5678 | CX=1234 DX=5678 |

| R0->R2 | CX=1234 DX=5678 | CX=1278 DX=5678 | CX=1234 DX=5634 | CX=1234 DX=5678 | CX=1234 DX=5678 | CX=7878 DX=5678 | CX=1234 DX=5634 | CX=1234 DX=5678 |

| R0->R3 | CX=1234 DX=5678 | CX=1256 DX=5678 | CX=1234 DX=3478 | CX=1234 DX=5678 | CX=1234 DX=5678 | CX=5656 DX=5678 | CX=1234 DX=1278 | CX=1234 DX=5678 |

| R1->R0 | CX=1234 DX=5678 | CX=3434 DX=5678 | CX=1212 DX=5678 | CX=1234 DX=5678 | CX=1234 DX=5678 | CX=3434 DX=5678 | CX=1212 DX=5678 | CX=1234 DX=5678 |

| R1->R1 | CX=1234 DX=5678 | CX=1234 DX=5678 | CX=1234 DX=5678 | CX=1234 DX=5678 | CX=1234 DX=5678 | CX=1234 DX=5678 | CX=1234 DX=5678 | CX=1234 DX=5678 |

| R1->R2 | CX=1234 DX=5678 | CX=7834 DX=5678 | CX=1234 DX=5612 | CX=1234 DX=5678 | CX=1234 DX=5678 | CX=7834 DX=5678 | CX=1234 DX=5612 | CX=1234 DX=5678 |

| R1->R3 | CX=1234 DX=5678 | CX=5634 DX=5678 | CX=1234 DX=1278 | CX=1234 DX=5678 | CX=1234 DX=5678 | CX=5634 DX=5678 | CX=1234 DX=1278 | CX=1234 DX=5678 |

| R2->R0 | CX=1234 DX=5678 | CX=1234 DX=5634 | CX=1278 DX=5678 | CX=1234 DX=5678 | CX=1234 DX=5678 | CX=1234 DX=3434 | CX=1278 DX=5678 | CX=1234 DX=5678 |

| R2->R1 | CX=1234 DX=5678 | CX=1234 DX=5612 | CX=7834 DX=5678 | CX=1234 DX=5678 | CX=1234 DX=5678 | CX=1234 DX=1212 | CX=5634 DX=5678 | CX=1234 DX=5678 |

| R2->R2 | CX=1234 DX=5678 | CX=1234 DX=5678 | CX=1234 DX=5678 | CX=1234 DX=5678 | CX=1234 DX=5678 | CX=1234 DX=7878 | CX=1234 DX=5678 | CX=1234 DX=5678 |

| R2->R3 | CX=1234 DX=5678 | CX=1234 DX=5656 | CX=1234 DX=7878 | CX=1234 DX=5678 | CX=1234 DX=5678 | CX=1234 DX=5656 | CX=1234 DX=5678 | CX=1234 DX=5678 |

| R3->R0 | CX=1234 DX=5678 | CX=1234 DX=3478 | CX=1256 DX=5678 | CX=1234 DX=5678 | CX=1234 DX=5678 | CX=1234 DX=3478 | CX=1256 DX=5678 | CX=1234 DX=5678 |

| R3->R1 | CX=1234 DX=5678 | CX=1234 DX=1278 | CX=5634 DX=5678 | CX=1234 DX=5678 | CX=1234 DX=5678 | CX=1234 DX=1278 | CX=5634 DX=5678 | CX=1234 DX=5678 |

| R3->R2 | CX=1234 DX=5678 | CX=1234 DX=7878 | CX=1234 DX=5656 | CX=1234 DX=5678 | CX=1234 DX=5678 | CX=1234 DX=7878 | CX=1234 DX=5656 | CX=1234 DX=5678 |

| R3->R3 | CX=1234 DX=5678 | CX=1234 DX=5678 | CX=1234 DX=5678 | CX=1234 DX=5678 | CX=1234 DX=5678 | CX=1234 DX=5678 | CX=1234 DX=5678 | CX=1234 DX=5678 |

结论:

1、000、011、100、111是假的。

2、由实验1和实验2可知,DX作为源寄存器的时候要求XP为1、DX作为目标寄存器的时候要求OP为0,因此,当且仅当W、XP、OP为0、1、0或者1、1、0的时候,才有可能实现任意通用寄存器到通用寄存器的赋值,其余情况都不可能完成。

3、对于010来说,是完全符合预期的结果,用给定的高低位覆盖了目标的高低位。对于110来说,部分指令的执行结果符合预期,但是也有部分指令(例如R2->R1)的结果是不正确的。

设计机器指令OUTL RD,实现将寄存器RD的值输出到OUT低8位。并验证RD如何作为源寄存器。参考上例,请自己设计表格,并得出结论。

CX和DX都有可能作为源寄存器,然而当且仅当XP为1的时候,源寄存器才会选择DX,否则无论RS是什么都只能选CX。对于本题来说,显然RD应该为CX或DX之一,因此,W、XP、OP的结果只剩下4种选择(010、011、110、111)。

因此,下面只需要对这4种可能做验证。

实验开始前,令寄存器CX=1234,令DX=5678。

| W|XP|OP取值 | 总线规则 | R0->OUT | R1-> OUT | R2-> OUT | R3-> OUT |

|---|---|---|---|---|---|

| 010 | 偶->奇 | 34FF | 12FF | 78FF | 56FF |

| 011 | 偶->偶 | FF34 | FF12 | FF78 | FF56 |

| 110 | 12FF | 12FF | 56FF | 56FF | |

| 111 | 字传递 | 1234 | 1212 | 5678 | 5656 |

观察上表结果,只有W、XP、OP取值为0、1、1时符合预期。

因此,微指令应该为,源编码选择RRD,目的编码选择IOW,总线规则为011。

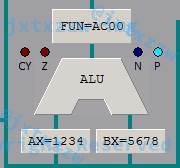

设计微程序(确切地说,只需要个别微指令),验证AX+BX运算时,W, XP 和 OP的作用。

实验开始前,设置AX=1234h,BX=5678h,观察在W, XP, OP取不同值时的结果。请自己设计表格,并得出结论。

这里与DX无关,所以需要对8种可能做尝试。

首先定义MYADD指令,执行AX+BX。

源编码选择ALU,目的编码暂时不需要,因为不需要输出,只是为了观察结果。

例如,W、XP、OP取值为0、0、0的时候,AX+BX的结果为AC00。

| W|XP|OP取值 | 总线规则 | AX+BX |

|---|---|---|

| 000 | 奇->奇 | AC00 |

| 001 | 奇->偶 | AC00 |

| 010 | 偶->奇 | 00AC |

| 011 | 偶->偶 | 00AC |

| 100 | 奇->奇 | AC00 |

| 101 | 奇->偶 | AC00 |

| 110 | 68AC | |

| 111 | 字传递 | 68AC |

结论:

1、 总线规则的源的奇偶决定了结果存放在ALU寄存器的高字节还是低字节。

2、 当总线规则为字节的时候,无论W、XP、OP值为多少,都是AX的低字节与BX的低字节相加。

3、 当总线规则为110或者111的时候,是整个AX与整个BX相加。

验证微指令RAM->IR时的散转下址0600是否可变。模型机中RAM->IR微指令的下址设置的都是0600,取指周期散转时,系统根据0600和IR的值经运算得到微程序入口地址。如果微指令RAM->IR的下址不是0600,那么微程序入口地址还是通过IR的值和0600运算得到吗?请设计实验和相关表格,并得出结论。

不能。

实验中,只要勾选IR,则自动变为取指变址。

此时无论如何设置微地址都不再有效。基址还是600H,所以最后微程序入口地址还是保持600H+IR的值。

111

感谢